Pong in an FPGA with VHDL

Project to implement the pong game in a Terasic FPGA through VHDL

During my last year of the Bachelor’s I had one course fully dedicated to understand and learn to program on an FPGA. The language that was used for this purpose was VHDL

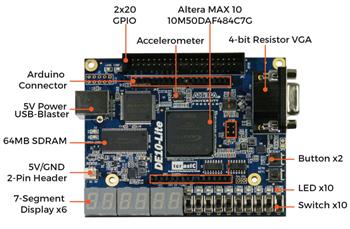

and the board that we used was the FPGA Max 10 DE10-Lite. This board contains an Altera MAX 10 FPGA.

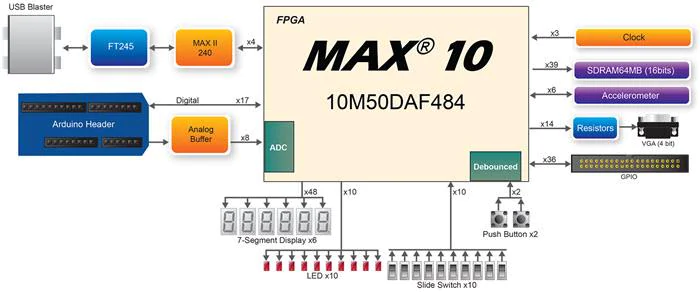

As you can see the board contains not only the FPGA, but also many peripherals to implement real applications and practice. Some of them can also be identified in this connection diagram:

We used the Intel Quartus Prime as the software editor and synthesizer to program the FPGA. The course was very practical and after many lab lessons, we had to develop a final project. For this project I decided to

implement the pong game in the FPGA so that I can get also familiar with one of the peripherals, the VGA interface. In a few words, this game contains a VGA driver for the FPGA an image generator and a score shown in 7-segment

displays. Many challenges that were fun to solve where the VGA driver where I got familiar on how an image is generated through this kind of interface and screens and also modelling the behaviour of the ball, collisions and how it bounces. The following video shows the game:

And this is the code of the project: